Module: Electronics, 3rd year

Digital Systems Design with

Hardware Description Languages

# Logic synthesis

- Introduction to the synthesis

- Synthesis of the basic elements

- Hardware representation of VHDL objects

- Synthesis of complex circuits

- Synthesis of types

- Non-synthesizable structures

- "A VHDL Synthesis primer" J.Bhasker,

- "VHDL A Logic Synthesis Approach" D. Naylor, S. Jones,

- "VHDL Coding and Logic Synthesis with SYNOPSIS" W.F.Lee,

- "Reuse Methodology Manual" M.Keating, P.Bricaud,

- "Synthesis and Simulation Design Guide" (Xilinx manual)

- "Xilinx Synthesis Technology (XST) User Guide" (Xilinx manual)

- "Digital System Design with VHDL" M.Zwoliński (translated: "Projektowanie układów cyfrowych z wykorzystaniem języka VHDL")

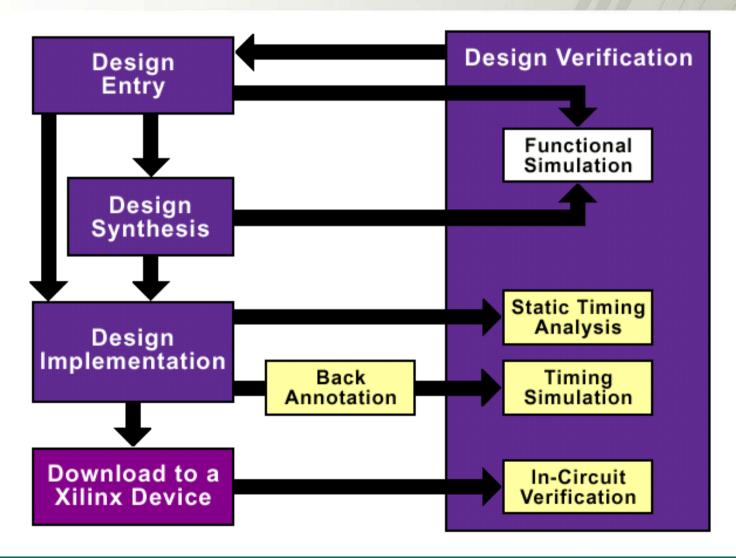

## Synthesis & implementation Xilinx CPLD/FPGA Design

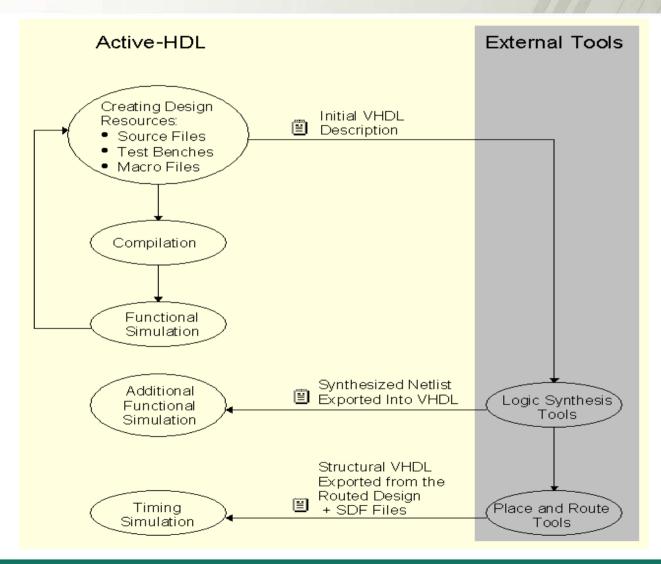

### Synthesis & implementation Design in Active-HDL environment

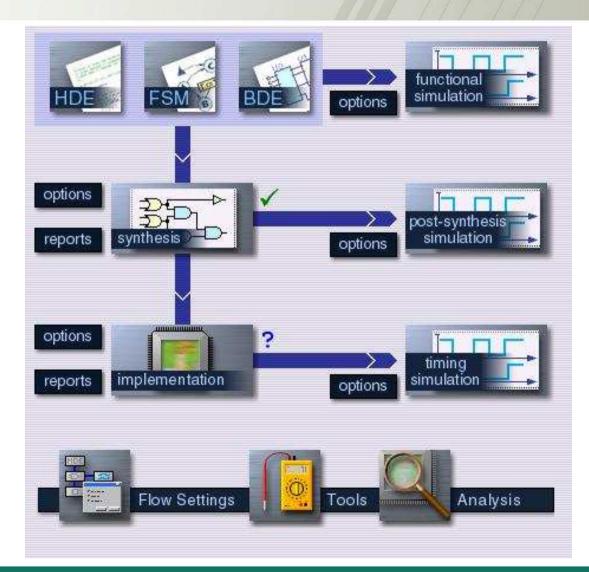

# Synthesis & implementation Design in Active-HDL environment: Design Flow

External tools for synthesis and implementation

**Graphical shell** by selecting option:

Tools/Preferences/ Environment/Flows/ Integrated Tools

and

View/Flow

### Synthesis of the basic elements **Arithmetic and logical operators**

```

architecture behavioral of AND gate is

begin

process (A, B)

-- synthesized AND gate

begin

if A = 1' and B = 1' then

X \leq \frac{1'}{2}

else

X \leq 0'

end if;

end behavioral;

architecture inferred of AND gate is

begin

-- inferred AND gate

-- from the library of

X \leq A \text{ and } B;

-- presynthesized elements

end inferred;

Inferred and or xor not nor nand xnor

<u>operators:</u> + - * / = /= > >= < <= ...

```

### Synthesis of the basic elements Tri-state buffer

```

architecture behavioral of TRI STATE buffer is

begin

process (A, OE)

begin

if OE = '1' then

OE

X \leq A;

else

X \leq X';

end if;

end behavioral;

architecture inferred of TRI STATE buffer is

begin

X \le A when OE = '1' else 'Z';

end inferred;

```

### Synthesis of the basic elements **Priority encoder**

```

architecture concurrent of PRIORITY encoder is

begin

code \leq "0001" when sel(0) = '1' else

"0010" when sel(1) = '1' else

"0100" when sel(2) = '1' else

"1000" when sel(3) = '1' else

"0000";

end concurrent;

so-

c_0 = s_0

S<sub>1</sub>

c_1 = \bar{s}_0 s_1

ar{\mathtt{s}_{\scriptscriptstyle{1}}}

c_2 = \bar{s}_0 \bar{s}_1 s_2

s_2

c_3 = \overline{S_0} \overline{S_1} \overline{S_2} S_3

► C3

s_3

```

#### **Note the logical functions implemented in LUTs!**

### Synthesis of the basic elements **Priority encoder**

```

architecture behavioral of PRIORITY encoder is

begin

process (A, B, C)

begin

if A = 1' then -- A: signal coming with

X <= '1'; -- large delay

elsif B = 1' then

X \ll 0';

elsif C = 1' then

X \leq 1';

else

X \leq 0;

end if;

B

end behavioral;

```

Note the logical functions implemented in LUTs!

# An object - signal or variable - may be represented as:

- flip-flop (edge-triggered memory element)

- latch (level-triggered memory element)

- wire (combinatorial element)

# Logic synthesis Hardware representation of VHDL objects

```

if C = 1 and

C'event

then

Q <= A;

end if;

signal Q:

flip-flop</pre>

```

```

if C = 1then

Q <= A;

else

-- do nothing

end if;

signal Q:

latch</pre>

```

```

if C = 1 then

Q \leq A;

else

Q \leq B;

end if;

signal Q:

multiplexer

```

### Hardware representation of objects Synthesis of D-type flip-flop

#### **Process containing sensitivity list:**

#### Process containing wait statement

#### Do not combine edge detection with other conditions:

```

if CLK'event and CLK = '1' and CE = '1' then ...

```

#### **Concurrent conditional assignment (not recommended):**

```

Q <= A and B when CLK'event and CLK = '1';

```

### Hardware representation of objects Flip-flop with Clock Enable input

```

GATECLK <= IN1 and IN2 and CLK;

process (GATECLK)

begin

if GATECLK'event and GATECLK = '1' then

if LOAD = 1' then

OUT1 <= DATA;

end if:

end if;

end process;

DATA

DFF

OUT1

LOAD

CE

IN1

GATECLK

IN2

C

CLK

```

AND3

# Hardware representation of objects Flip-flop with Clock Enable input

```

ENABLE <= IN1 and IN2 and LOAD;

process (CLK)

begin

if CLOCK'event and CLOCK = '1' then

if ENABLE = 1' then

OUT1 <= DATA;

end if;

D

end if;

CE

end process;

DATA

DFF

IN1

OUT1

Q

IN2

ENABLE

CE

LOAD

AND3

CLOCK

C

```

## Hardware representation of objects Synthesis of Set / Reset inputs

```

process (CLK)

begin

if CLK and CLK'event then

if SET = '1' then -- synchronous SET

Q \leftarrow 1';

else

O \leq A \text{ and } B;

end if:

end if:

end process;

process(CLK, RESET) -- RESET in sensitivity list!

begin

if RESET = '1' then -- asynchronous RESET

0 <= '0';

elsif CLK and CLK'event then

Q \leq A \text{ and } B;

end if;

end process;

```

### Hardware representation of objects Synthesis of D-type latch

#### **Process containing sensitivity list:**

```

process (CLK, A, B) -- list of all signals...

begin -- ...used in the process

if CLK = '1' then -- active high

Q <= A and B;

end if;

end process;</pre>

```

#### **Concurrent conditional assignment (not recommended):**

```

Y \le A and B when CLK = '1';

```

### Hardware representation of objects Unintentional synthesis of latch

```

process (A, B, C, SEL)

begin

if SEL = "00" then

Y <= A;

elsif SEL = "01" then

Y <= B;

elsif SEL = "10" then

Y <= C;

end if;

end process;</pre>

```

#### **Problem:**

synthesis of latch as a result of incomplete specification of options (for **SEL** = "11" combination, the last value will be hold by default, which will imply a memory element).

```

process (A, B, C, SEL)

begin

if SEL = "00" then

Y <= A;

elsif SEL = "01" then

Y <= B;

elsif SEL = "10" then

Y <= C;

elsif SEL = "11" then

Y <= '0';

end if;

end process;</pre>

```

#### **Solution:**

specifying all the possibilities (also in the case statement - here you can use the *default* specification clause when others).

### Hardware representation of objects **Signals and variables**

```

signal A,B,C,D: bit

TMP

NO MEMORY: process (A,B,C)

B

variable TMP: bit;

begin

TMP := A and B;

Synthesis of TMP: wire

D \ll TMP \circ C;

end process;

signal A,B,C: bit

IS IT LATCH: process (A,B,C)

variable TMP: bit;

begin

C \leq TMP \text{ and } B;

TMP := A or C;

Synthesis of TMP : <u>latch ?!</u>

end process;

```

### Hardware representation of objects Signals and variables

```

signal Qaux: ...

Qaux

Q

FFx2: process (clk)

begin

Qaux <= D;

clk

Q \le Qaux;

end process;

Synthesis: 2 flip-flops

FFx1: process (clk)

Qaux

variable Qaux: ...

begin

Qaux := D;

clk ·

Q \le Qaux;

end process;

Syntesis: 1 flip-flop

```

# Synthesis of complex circuits Logical operators

```

entity logical_ops is

port (a, b, c, d: in bit; m: out bit);

end logical_ops;

architecture example of logical_ops is

signal e: bit;

begin

m <= (a and b) or e;

e <= c xor d;

end example;</pre>

```

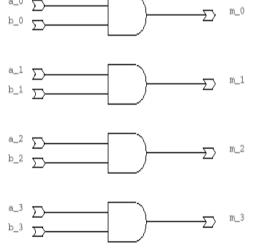

```

entity logical_bit is

port (a, b: in bit_vector (0 to 3);

m: out bit_vector (0 to 3));

end logical_bit

architecture example of logical_bit is

begin

m <= a and b;

end example;</pre>

```

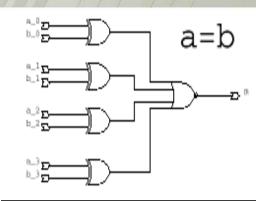

# Synthesis of complex circuits Relational operators

```

entity relational_equ is

port (a, b: in bit_vector (0 to 3);

m: out boolean);

end relational_equ;

architecture example of relational_equ is

begin

m <= a = b;

end example;</pre>

```

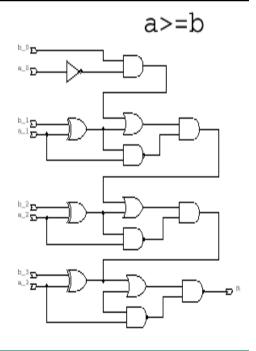

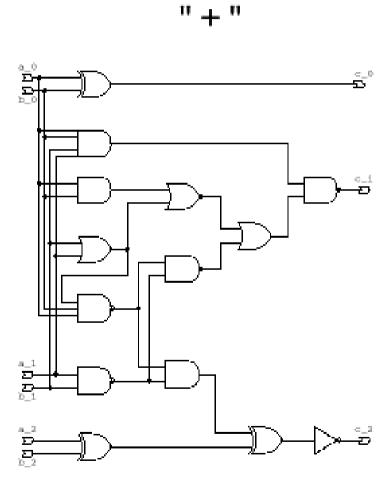

# Synthesis of complex circuits Arithmetic operators

```

package example arithmetic is

type small int is range 0 to 7;

end example arithmetic;

use work.example arithmetic.all;

entity arith is

port (a, b: in small int;

m: out small_int);

end arith;

architecture example of arith is

begin

m \le a + b;

end example;

```

### Note the hard-macros of adders (and multipliers!)

### Synthesis of complex circuits Selection statements

#### **Sequential selection statements**

- conditional signal assignment: if . . .

- selected signal assignment: case...

#### **Concurrent selection statements**

- conditional signal assignment: when . . .

- selected signal assignment: with...

#### **Synthesis of complex circuits**

### Sequential selection statements: if

```

entity control stmts is

port (a, b, c: in boolean; m: out

boolean);

end control stmts;

architecture example of control stmts

is

begin

process (a, b, c)

variable n: boolean;

begin

if

if a then

n := b;

else

n := c;

end if:

m \le n;

end process;

end example;

```

#### **Synthesis of complex circuits**

### **Sequential selection statements: case**

```

entity control stmts is

port (sel: bit vector (0 to 1); a,b,c,d: bit;

m: out bit);

end control stmts;

architecture example of control stmts is

case

begin

process (sel,a,b,c,d)

begin

case sel is

when b"00" => m <= c;

when b"01" => m <= d;

when b"10" => m <= a;

when others => m <= b;</pre>

с

Г

end case;

end process;

end example;

```

#### **Synthesis of complex circuits**

### Concurrent selection statements: when / with

```

entity control stmts is

port (a, b, c: in boolean; m: out boolean);

end control_stmts;

architecture example of control stmts is

begin

m \le b when a else c:

end example;

entity control stmts is

port (sel: bit_vector (0 to 1); a,b,c,d: bit; m: out bit);

end control stmts;

architecture example of control stmts is

begin

with sel select

m \le c \text{ when } b"00"

m \le d when b"01",

m \le a when b"10",

m <= b when others;

end example;

```

# Synthesis of complex circuits Logic replication – loop

```

entity loop stmt is

port (a: bit vector (0 to 3);

m: out bit_vector (0 to 3));

end loop stmt;

architecture example of loop stmt is

begin

loop

process (a)

variable b: bit;

8.__0

begin

b := '1';

for i in 0 to 3 loop

a\_1

b := a(3-i) \text{ and } b;

m(i) \le b;

end loop;

m_{\perp}1

end process;

m\_0

end example;

```

### Synthesis of complex circuits Logic replication - subprogram

```

entity subprograms is

port (a: bit vector (0 to 2);

m: out bit vector (0 to 2));

end subprograms;

architecture example of subprograms is

function simple (w, x, y: bit) return bit is

begin

return (w and x) or y;

subprogram

end:

begin

process (a)

begin

m(0) \le simple(a(0), a(1), a(2));

m(1) \le simple(a(2), a(0), a(1));

a_2

∑-

m(2) \le simple(a(1), a(2), a(0));

end process;

end example;

```

### Synthesis of complex circuits Shifters

#### **Sequential (shift register):**

with concatenation operator (&)

```

shreg <= shreg (6 downto 0) & SI;</pre>

```

• with loop statemnet for...loop

```

for i in 0 to 6 loop

shreg(i+1) <= shreg(i);

end loop;

shreg(0) <= SI;</pre>

```

• with shift operators (sll, srl, ...)

#### **Combinatorial (barrel shifter):**

• with shift operators (sll, srl, ...)

```

with SEL select

SO <= DI when "00",

DI sll 1 when "01",

DI sll 2 when "10",

DI sll 3 when others;</pre>

```

• with concatenation operator (&)

### Synthesis of complex circuits **Memories**

- inferred or instantiated

- implemented as a distributed or block memories (depending on the size, speed and occupied area)

- synchronous (optionally with asynchronous read distributed)

- RAM (also initialized) or ROM

- also used for combinatorial logic and FSMs

| Method                  | Advantages                                                                                                                                                  | Disadvantages                                                                                                                                                          |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inference               | Most generic way to incorporate<br>RAMs into the design, allowing<br>easy/automatic design migration<br>from one FPGA family to another     FAST simulation | <ul> <li>Requires specific coding styles</li> <li>Not all RAMs modes are supported</li> <li>Gives you the least control over implementation</li> </ul>                 |

| CORE Generator software | Gives more control over the RAM creation                                                                                                                    | May complicate design migration<br>from one FPGA family to another     Slower simulation comparing to<br>Inference                                                     |

| Instantiation           | Offers the most control over the implementation                                                                                                             | Limit and complicates design<br>migration from one FPGA family<br>to another     Requires multiple instantiations<br>to properly create the right RAM<br>configuration |

- Types and subtypes, which may represent negative values in range, are encoded in the Two's Complement code.

- Types and subtypes, which represent only positive values in range, are encoded in the Natural Binary Code.

- The number of bits used depends on the largest allowable value for the object.

```

-- binary encoding having 7 bits

type int0 is range 0 to 100;

type int1 is range 10 to 100;

-- 2's complement encoding having 8 bits (including sign)

type int2 is range -1 to 100;

-- binary encoding having 3 bits

subtype int3 is int2 range 0 to 7;

```

```

type short is integer 0 to 255;

subtype shorter is short range 0 to 31;

subtype shortest is short range 0 to 15;

signal op1, op2, res1: shortest;

signal res2: shorter;

signal res3: short;

begin

res1 <= op1 + op2; -- truncate carry

res2 <= op1 + op2; -- use carry

res3 <= op1 + op2; -- use carry and zero extend

```

#### **Declaration:**

#### ... is synthesized as:

```

-- the encoding of 11 is a "don't care"

subtype mem op is cpu op range load to store; -- two wires

-- the encodings of 00 and 11 are "don't cares"

-- User Defined Encoding

attribute enum encoding: string;

attribute enum encoding of cpu op: type is

"001" & -- execute

"010" & -- load

"100"; -- store

```

## Synthesis of types Enumerated and other types

- During synthesis the enumerated types are coded binary by default. Subsequent elements (L) of the enumerated type receive subsequent values, the first from the left receives value zero.

- Number of bits (N) of an object that represents the enumerated type will be the smallest possible number, satisfying the condition: L <= 2<sup>N</sup>

- bit & boolean types are synthesized as scalar

- character type is synthesized as 8-bit vector

#### Recommended, because:

- large number of values (9), describing most of the real states in digital systems,

- is automatically initialized to the value of 'U' this forces a designer to initialize objects explicitly. Do not overcome this feature by initialization of signals and variables in their declaration circuit that cannot be initialized may be obtained after synthesis in the result of such an approach.

- easy integration with other modules eg. integer type can be synthesized, but the simulation will require executing time-consuming conversion functions.

- <u>after synthesis and implementation there is only</u>

<u>std\_logic type</u>

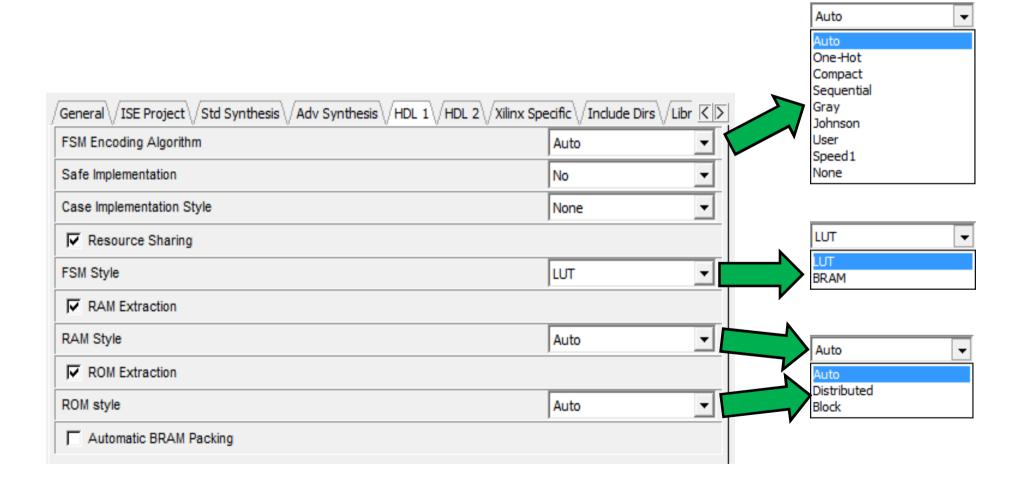

### Synthesis of FSMs FSM states encoding algorithms

- Auto

selects the needed optimization algorithms during the synthesis process

- One-Hot

ensures that an individual state register is dedicated to one state. Only one flip-flop

is active (hot) at any time. Very appropriate with most FPGAs where a large number

of flip-flops are available. Also a good alternative to optimize speed or to reduce power.

- Compact minimizes the number of state variables and flip-flops. Appropriate when optimizing area.

- Sequential consists of identifying long paths and applying successive radix two codes to the states on these paths. Next state equations are minimized

- Gray

guarantees that only one state variable switches between two consecutive states.

Appropriate for controllers exhibiting long paths without branching

- *Johnson* much like Gray option. Shows benefits with FSM containing long paths with no branching.

- User

causes the synthesis tool to use the encoding defined in the source file

- Speed1 oriented for speed optimization. The number of bits for a state register depends on the particular FSM, but generally it is greater than the number of FSM states.

- timing clauses:

- assignments (after, transport, inertial)

- wait for

- floating-point data types (real)

- file operations reduced:

- read: memory initialization from file

- write: debug