Module: Electronics & Telecomunication, 5rd year Programmable Logical Devices

# **Gallop cross VHDL**

Rajda & Kasperek © 2017 Dept. of Electronics, AGH UST

# Agenda

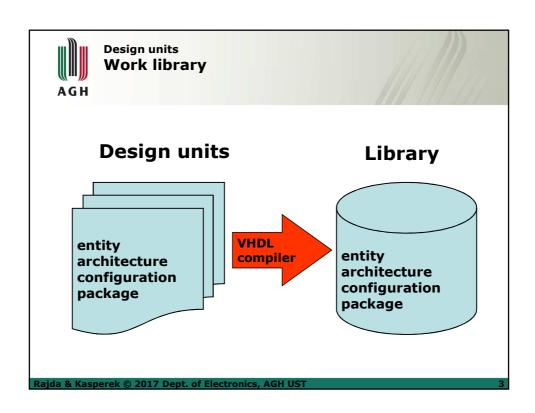

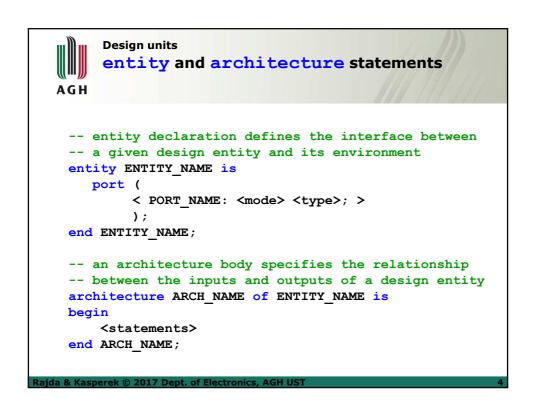

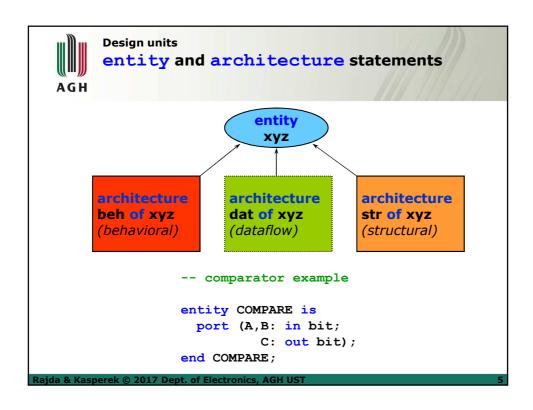

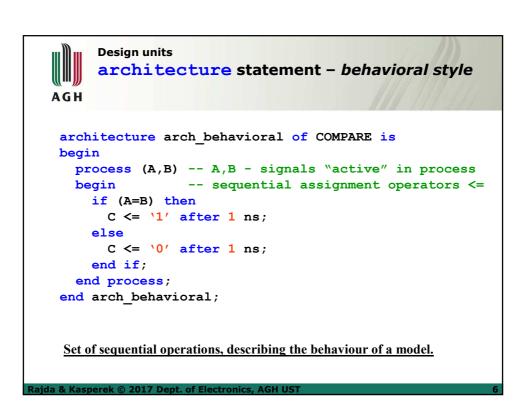

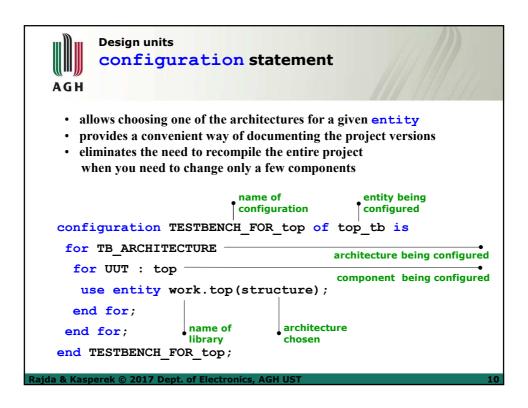

## **Design units**

entity, architecture, configuration, package

#### **Lexical elements**

literals, identifiers, objects, expressions

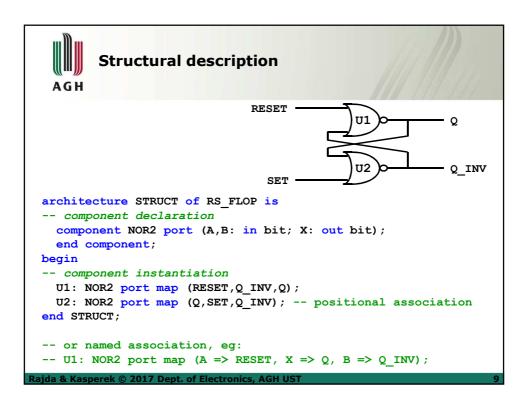

## **Structural description**

map, generate

### Sequential statements

process, wait, if, case, loop, next, exit, assert, function, procedure

#### **Concurrent statements**

assignments: unconditional, conditional and selected, subprograms,  $\mathtt{block}$

### Composite types

arrays: one-dimensional and multidimensional

Rajda & Kasperek © 2017 Dept. of Electronics, AGH UST

\_

#### **Design units**

architecture statement - dataflow style

```

architecture arch_dataflow of COMPARE is

begin - concurrent assignment operators <=

C <= not (A xor B) after 1 ns;

end arch_dataflow</pre>

```

Set of concurrent assignments, describing the flow of data.

Raida & Kasperek © 2017 Dept. of Electronics, AGH UST

#### **Design units**

architecture statement - structural style

```

architecture arch_structural of COMPARE is

signal I: bit;

component XOR2 port (x,y: in bit; z: out bit);

end component;

component INV port (x: in bit; z: out bit);

end component;

begin

U0: XOR2 port map (A,B,I);

U1: INV port map (I,C);

end arch_structural;

```

Set of connected modules, describing the structure of a model.

Rajda & Kasperek © 2017 Dept. of Electronics, AGH UST

### **Design units**

# package statement

Groups together the common: declarations, subprograms, components or types.

```

package my_constans is

constant unit_delay: time := 1 ns;

end my_constans;

Y <= '0' after work.my_constans.unit_delay;</pre>

```

### package STANDARD

In every VHDL tool, this package defines, among others, data types, such as: bit, boolean, bit\_vector, character, string, text etc.

Raida & Kasperek © 2017 Dept. of Electronics, AGH UST

11

# **Lexical elements**

# literals

inscriptions which represent the data, the way they are written implies all their properties, including their value

### • identifiers (names)

strings of letters and digits, identifying the objects

## objects

signals, variables, constants, parameters

## expressions

formulas including operators and arguments, determining the way of calculation or specification of values

Rajda & Kasperek © 2017 Dept. of Electronics, AGH UST

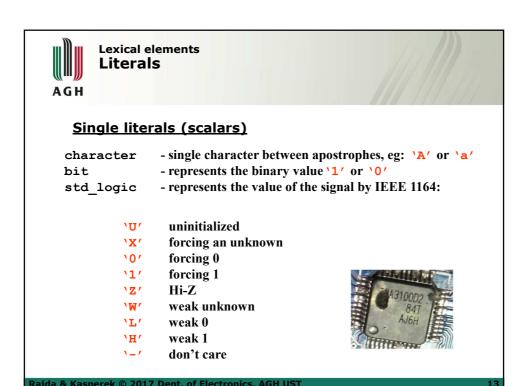

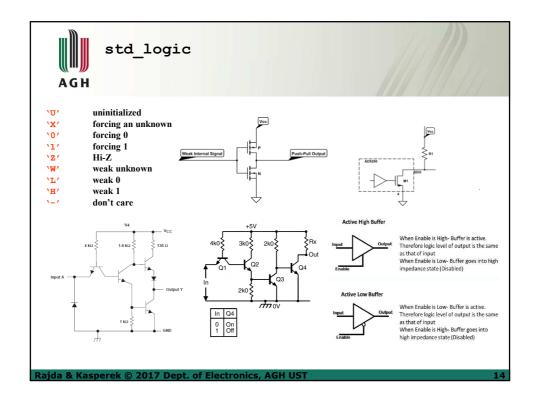

#### **Lexical elements** Literals

boolean - represents two discrete values:

```

true TRUE True

false FALSE False

real - represents a floating-point value, eg: 1.3 or

-344.0E+23, typically from -1.0E+38 to 1.0E+38

with a precision of at least six digits after the decimal point

integer - represents an integer value, eg: +1, 862 or -257,

+123 456, 16#00FF#, typically from -2, 147, 483, 647 to

+ 2,147,483,647

time - represent the only physical quantity defined, i.e. time:

62 fs, (ps, ns, us, ms, sec, min, hr)

```

# Multiple literals (arrays, vectors)

```

string - string of characters, covered by quotes, eg: "x", "T hold"

bit vector - "0001 1100", x"00FF"

std_logic_vector-"101z", "UUUUUU"

```

### **Lexical elements** Literals

#### **Decimal literals: Based literals:** -- 254 14 16#FE# 7755 2#1111 1110# -- 254 156E7 8#376# -- 254 188.993 16#D#E1 -- 208 88\_670\_551.453\_909 16#F.01#E+2 -- 3841.00 2#10.1111\_0001#E9 -- 1506.00 44.99E-22 **Physical literals:** 60 sec

100 m 5 kohm 177 A

b"11111110" **B"1111\_1110"** - equivalent binary representation x"FE" 0"376"

- binary representation

- equivalent hexadecimal representation

- equivalent octal representation

#### **Lexical elements Identifiers, ranges**

#### **Basic identifiers**

Must begin with a letter. Subsequently there may occure letters, numbers or underscore ( \_ ). Underscore may not be the last character, nor there may be two neighbouring underscores. VHDL is not the case sensitive: XYZ <=> xyz. Identifiers may not be the same as keywords (approximately 100).

Example: XYZ, X3, S(3), S(1 to 4),  $my_defs$ .

The range of variability of the type can be limited:

```

range {low_val to high_val | high_val downto low_val}

np: integer range 1 to 10;

real range 1.0 to 10.0;

```

# **Lexical elements**

# **Declarations, signal declarations**

Most of the objects must be declared explicitly. Some objects (eg, iteration identifiers in a loop, signals arising from other signals by the use of attributes) are declared implicitly.

Declaration of objects (their names and types) include declarations of: constants, variables, signals, or files.

### **Signal declarations**

```

• scalar: signal name(s): type[range][:= expression];

• array: signal name(s): array type [(index)][:= expression];

• as a port (eg, scalar):

```

port (name(s): direction type [range][:= expression];...);

#### **Lexical elements** Variable declarations

# **Variable declarations (within the process)**

```

• scalar:

```

```

variable name(s): type[(range)][:= expression];

```

### • array:

```

variable name(s): array type [(range)][:= expression];

```

#### eg:

```

variable Index: integer range 1 to 50;

variable Adder Delay: time range 10ns to 50ns := 10ns;

variable MEMORY: bit vector (0 to 7);

variable x,y: integer;

```

VHDL'93 introduced a shared variable for communication between processes.

### **Lexical elements Expressions**

## **Arguments of expressions must respond** in terms of the types

#### **Types coversions:**

```

integer (3.0)

=>

integer

real (3)

=>

real

integer * time

time

=>

nanos + picos

time

nanos / picos

integer

variable My_Data, My_Sample: integer;

My_Data := integer(74.94 * real(My_Sample));

Vector <= CONV_STD_LOGIC_VECTOR(Integer_Variable);</pre>

```

# Lexical elements Operators

AGH

## **Operators in expressions:**

logical and or nand nor xor not

relational = /= < <= > >=

concatenation &

arithmetic + - \* / \*\*

mod rem abs

shift ('93) sll srl sla sra rol ror xnor

### **Required types of arguments:**

the same : and or nand nor xor not

= /= < <= > >= + - \* /

integer : mod rem

integer exp : \*\*

numerical : abs

Raida & Kasperek © 2017 Dept. of Electronics, AGH UST

21

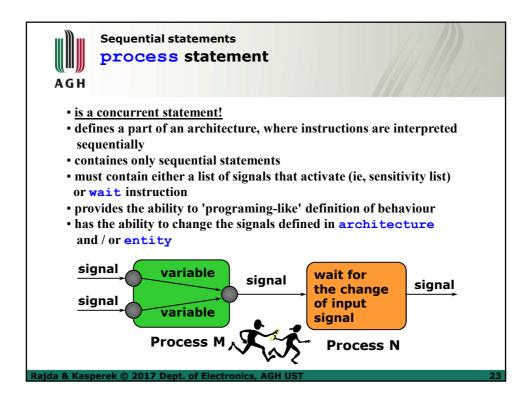

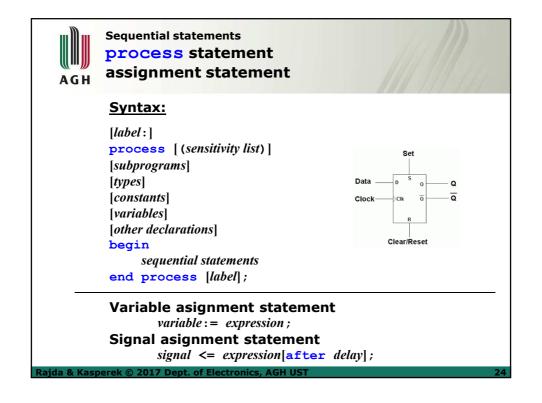

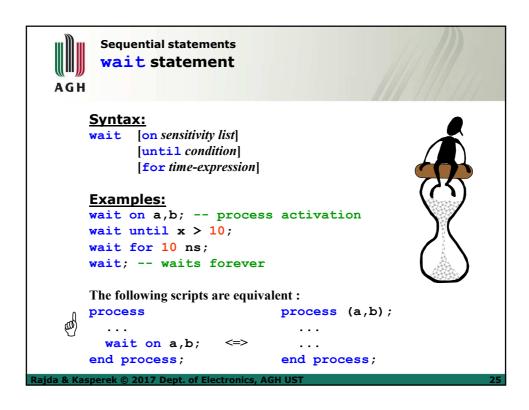

# **Sequential statements**

- process (concurrent!)

- sequential assignment

- wait

- if

- case

- null

- loop

- next

- exit

- assert

- subprograms

Rajda & Kasperek © 2017 Dept. of Electronics, AGH UST

```

Sequential statements

if statement

Syntax:

if condition then sequential_statements;

[elsif condition then sequential_statements];

[else sequential_statements];

end if;

Example:

process(R, CLK)

begin

if R = '0' then

operand(7 downto 0) <= "000000000";

elsif CLK = '1' and CLK'event then

operand(7 downto 0) <= DATAB;</pre>

end if;

end process;

```

# Sequential statements

case statement

Especially convenient to decode: the codes, the states of finite state machine or the buses states.

#### **Syntax:**

```

case BCD_int is

when 0 => LED <= "1111110";

when 1 => LED <= "0110000";

...

end case;</pre>

```

Rajda & Kasperek © 2017 Dept. of Electronics, AGH UST

27

# **Concurrent statements**

- signal assignment statements

- unconditional

- conditional

- selected

- subprograms

- block

Rajda & Kasperek © 2017 Dept. of Electronics, AGH UST

# Concurrent statments Unconditional signal assignment

In both examples below, the result of the assignment is the same:

```

architecture sequential of MULTIPLEXER is

begin

process (A,INDEX)

begin

OUTPUT <= A (INDEX); -- sequential

end process;

end sequential;

architecture concurrent of MULTIPLEXER is

begin

OUTPUT <= A (INDEX); -- concurrent

end concurrent;</pre>

```

Raida & Kasperek © 2017 Dept. of Electronics, AGH UST

20

# Concurrent statments Conditional signal assignment

#### **Syntax:**

signal <= {expression when condition else} expression;</pre>

### **Example:**

```

DATA <= ROM when ADR < x"2000" else

RAM when ADR < x"6000" else

"ZZZZZZZZ";

```

Analogous to the sequential if statement, but:

- execute without taking the order into account,

- used in dataflow i structural description styles,

- are synthesizes to the combinational logic.

Note! Can not be used inside the process.

Rajda & Kasperek © 2017 Dept. of Electronics, AGH UST

# Concurrent statments Selected signal assignment

### **Syntax:**

```

with expression select

signal <= {expression when choices,};</pre>

```

### **Example:**

Note! Can not be used inside the process.

Raida & Kasperek © 2017 Dept. of Electronics, AGH UST

21

# **Advanced data types**

- Predefined types

- Extended Types

- Enumerated Types

- Subtypes

- Composite Types

- Arrays

- one-dimensional (vectors)

- multidimensional

- Records

- Other Predefined Types

- Files

- Lines

Rajda & Kasperek © 2017 Dept. of Electronics, AGH UST

#### Advanced data types Arrays

AGE

- Consist of elements of the same type.

- Used to describe the buses, registers and other sets of hardware components.

- Array elements can be scalars or other composite objects. (It is not possible to create eg arrays of files!)

- Access to the specific elements through the use of pointers.

The only <u>predefined</u> array types are:

- bit\_vector (package STANDARD)

- string (package STANDARD)

- std\_logic\_vector (package STD\_LOGIC\_1164)

If needed, the user has to declare the new types of arrays for the real and integer elements himself.

Rajda & Kasperek © 2017 Dept. of Electronics, AGH UST

22

# Advanced data types – Arrays Vectors – index range declaration

The way of access depends on the way of declaration.

#### **Examples:**

d(3) d(2) d(1) d(0)  $b(4 \ to \ 7) \qquad \text{any range}$   $c(4) \qquad \qquad \text{index out of range}$

c (1.0) wrong type of index

Rajda & Kasperek © 2017 Dept. of Electronics, AGH UST

# Advanced data types - Arrays **Vectors - assignments**

AGH

Example: for the bit\_vector type:

```

c := "1010"; constant of the bit_vector type

c := x"A"; as above, note the length!

c := S & T & M & W; 4 concatenated 1-bit signals

c := ('1', '0', '1', '0'); 4-bit aggregate

c := 10; forbidden

```

#### **Vector slices**

Assignments may be executed between the slices (fragments) of vectors.

#### **Examples:**

```

variable a: bit_vector (3 downto 0);

variable c: bit_vector (8 downto 1);

c(6 downto 3) := a;

c(6 downto 3), not the c(3 to 6) - direction of the indexes must be the same as in the declaration!

```

Raida & Kasperek © 2017 Dept. of Electronics, AGH UST

**2** E

# Advanced data types – Arrays Vectors – aggregates

Literal may contain a list of array elements in <u>positional</u> and / or <u>named</u> association, creating the so-called aggregate.

#### **Syntac:**

```

[type_name'] ([choice =>] expression1 {, [others =>] expression2})

```

#### **Examples:**

```

variable a,b: bit := '1';

variable x,y: bit_vector (1 to 4);

-- positional association

x := bit_vector'('1',a nand b,'1',a or b);

-- named association

y := (1 => '1', 4 => a or b,2 => a nand b,3 => '1');

=> read: "receives"

```

Rajda & Kasperek © 2017 Dept. of Electronics, AGH UST

Using the named association, [choice =>] points to the one or many elements.

[choice =>] may include an expression (eg: (i mod 2) => ), pointing to one element or contain the range (eg: 3 to 5 => or 7 downto 0 => ), pointing to the sequence of elements.

The positional association has to be used before the named one.

#### **Example:**

```

variable b: bit;

variable c: bit_vector (8 downto 1);

c := bit_vector'('1',b,5 downto 2 =>'1',others =>'0');

```

### Very convenient and frequently used:

```

Counter <= (others => '0');

Data Bus <= (others => 'Z');

```

Raida & Kasperek © 2017 Dept. of Electronics, AGH UST