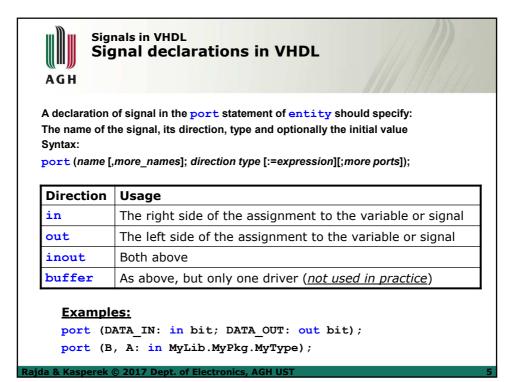

| Signals in VHDL<br>Signal declarations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | in VHDL                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>Global signals:<br/>package SIGDEC is<br/>signal RESET: bit := '1';<br/>signal INIT: bit := '0';<br/>end SIGDEC;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <pre>Signals global for entity:<br/>entity BOARD_DESIGN is<br/>port (DATA_IN: in bit;<br/>DATA_OUT: out bit);<br/>signal SYS_CLK: bit := '1';<br/>end BOARD_DESIGN;</pre>                           |

| Signals local for architecture:<br>architecture DATA_FLOW of BOAR<br>signal INT_BUS: bit;<br>begin<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D_DESIGN is<br>SignalAssignments_1<br>CODEC_1MHz < <clk_1mhz '0';<="" (codec_clk_en="1" )="" else="" th="" when=""></clk_1mhz>                                                                      |

| CLK_48MHz CLK_48MHz<br>AVR_RESET U<br>U1<br>CLK_48MHz<br>U1<br>CLK_48MHz<br>U1<br>CLK_48MHz<br>U1<br>CLK_48MHz<br>U1<br>CLK_48MHz<br>U1<br>CLK_48MHz<br>U1<br>CLK_48MHz<br>U1<br>CLK_48MHz<br>U1<br>CLK_48MHz<br>U1<br>CLK_48MHz<br>U1<br>CLK_48MHz<br>U1<br>CLK_48MHz<br>U1<br>CLK_48MHz<br>U1<br>CLK_48MHz<br>CLK_48MHz<br>U1<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHz<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLK_48MHZ<br>CLKA<br>CLK_48MHZ<br>CLKA<br>CLK_48MHZ<br>CLK_48MHZ | CODEC_IMPZ~CCLK_IMPZ_WIER(COLEC_CLFIF-Tylese 0;<br>CAX_T2MHZ~CCLK_IMPMen(CIX_CLK_EN='1) else 0;<br>CAX_T2MHZ~CCLK_IMPZ benching<br>CODEC_IMPZ<br>CCLK_24MHZ<br>CLK_24<br>CLK_24<br>CLK_24<br>CLK_24 |

```

Signals in VHDL

Zero delay

AGH

Example:

entity VAR is

port (A: in bit_vector (0 to 7);

INDEX: in integer range 0 to 7;

OUTPUT: out bit);

end VAR;

architecture VHDL 1 of VAR is

begin

process

begin

OUTPUT <= A(INDEX); -- 0 ns delay

-- wait initializes the assignment

wait ....;

. . . . .

end VHDL 1;

ajda & Kasperek © 2017 Dept. of Electronics, AGH U

```

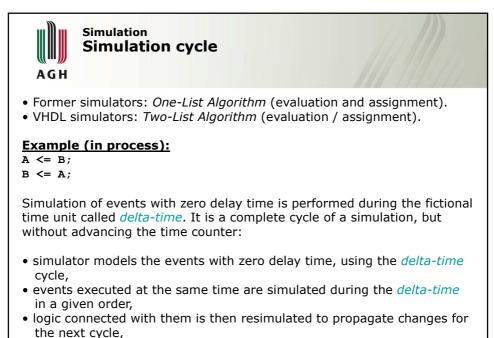

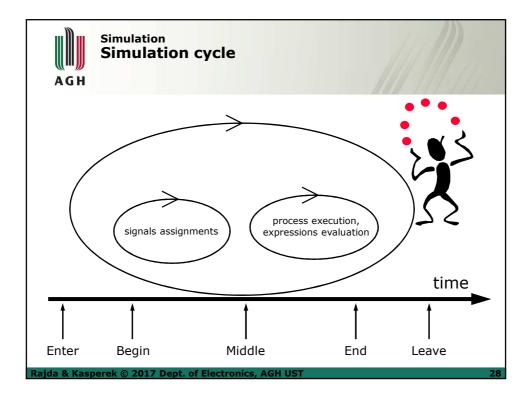

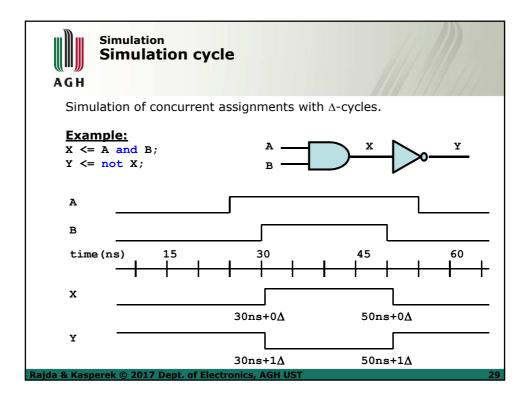

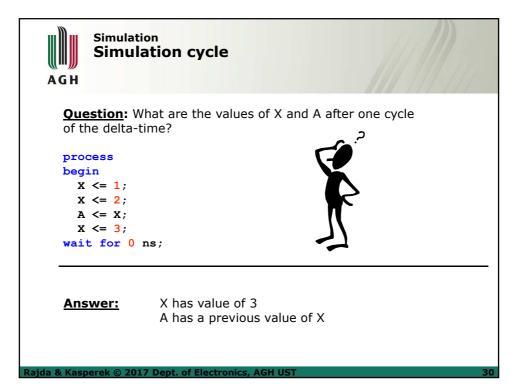

• delta-time cycles are repeated until no changes are detected.

ijda & Kasperek © 2017 Dept. of Electronics, AGH UST

| Simulation<br>Resolution fu                                                                                                                                           | nction                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| architecture SEQUENTIAL o<br>signal Ain,Bin,Asel,Bse<br>begin                                                                                                         |                                                                                                                                                                                                                         |

| <pre>A:process (Ain,Asel) begin Sout &lt;= 'Z'; if (Asel='1') then Sout &lt;= Ain; end if; end process;</pre>                                                         | Asel<br>Ain<br>Bsel<br>Bin                                                                                                                                                                                              |

| <pre>B:process (Bin,Bsel) begin Sout &lt;= 'Z'; if (Bsel='1') then Sout &lt;= Bin; end if; end process; end SEQUENTIAL; Rajda &amp; Kasperek © 2017 Dept. of El</pre> | <pre>architecture CONCURRENT of TRISTATE is<br/>signal Ain,Bin,Asel,Bsel,Sout: STD_LOGIC;<br/>begin<br/>Sout &lt;= Ain when Asel = `1' else `Z';<br/>Sout &lt;= Bin when Bsel = `1' else `Z';<br/>end CONCURRENT;</pre> |

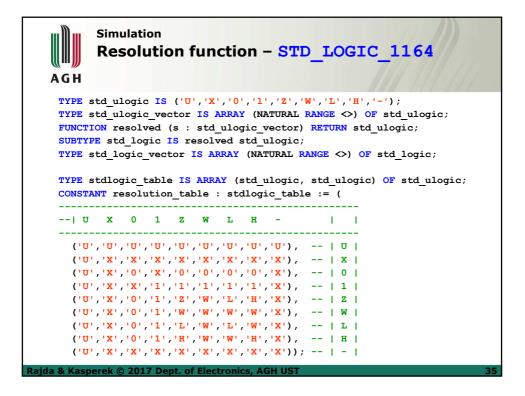

## Simulation **Resolution function – STD LOGIC 1164** AGH FUNCTION resolved (s: std\_ulogic\_vector ) RETURN std\_ulogic IS VARIABLE result : std ulogic := 'Z'; -- weakest state default BEGIN -- The test for a single driver is essential otherwise the -- loop would return 'X' for a single driver of '-' and that -- would conflict with the value of a single driver unresolved -- signal. IF (s'LENGTH = 1) THEN RETURN s(s'LOW); ELSE FOR i IN S'RANGE LOOP result := resolution\_table(result, s(i)); END LOOP; END IF: **RETURN** result; END resolved;

## Simulation Resolution function Function: returns one value, has all the arguments in input mode, passes the arguments by their values. Resolution function: is required when the signal (node) is controlled by more than one driver, performs the arbitration of signals, is invoked in case of change in any of the signal drivers, receives an array of signals for arbitration,

• is a user-defined function,

ek © 2017 Dept. of Electronics, AGH U

is associated with a subtype.

| GH Pre                                                                                                                                                                                                        | edefined attributes                                                                                                                         |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| Predefined<br>subprogra                                                                                                                                                                                       | attributes allow to get information about objects, types, ms, etc.                                                                          |  |

| Signal attribute                                                                                                                                                                                              | 25:                                                                                                                                         |  |

| Attribute                                                                                                                                                                                                     | Result                                                                                                                                      |  |

| S'Delayed(t)                                                                                                                                                                                                  | implicit signal, equivalent to signal S, but delayed t units of time                                                                        |  |

| S'Stable(t)                                                                                                                                                                                                   | implicit signal that has the value True when no event has occurred on S for t time units, False otherwise                                   |  |

| SQuiet(t) implicit signal that has the value True when no transaction has occurred on S for t time units, False otherwise                                                                                     |                                                                                                                                             |  |

| S'Transaction                                                                                                                                                                                                 | implicit signal of type Bit whose value is changed in each simulation cycle in<br>which a transaction occurs on S (signal S becomes active) |  |

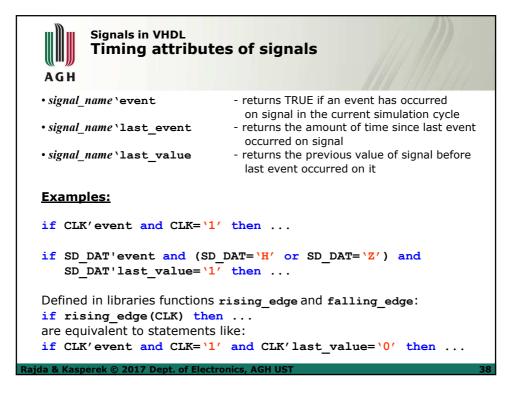

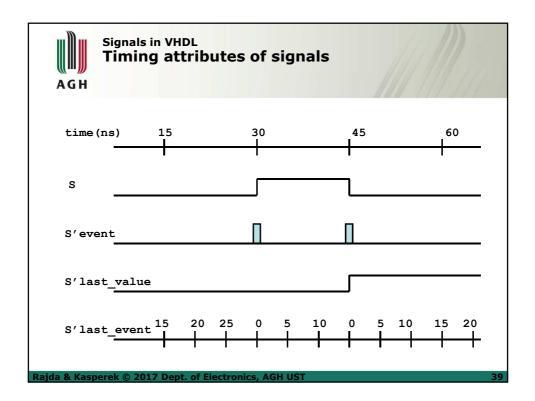

| S'Event                                                                                                                                                                                                       | True if an event has occurred on S in the current simulation cycle, False<br>otherwise                                                      |  |

| S'Active                                                                                                                                                                                                      | True if a transaction has occurred on S in the current simulation cycle, False<br>otherwise                                                 |  |

| SLast_event the amount of time since last event occurred on S, if no event has yet occurred it returns TimeHigh                                                                                               |                                                                                                                                             |  |

| S'Last_active                                                                                                                                                                                                 | Last_active the amount of time since last transaction occurred on S, if no event has yet<br>occurred it returns TimeHigh                    |  |

| S'Last_value                                                                                                                                                                                                  | the previous value of S before last event occurred on it                                                                                    |  |

| SDriving True if the process is driving S or every element of a composite S, or False if<br>the current value of the driver for S or any element of S in the process is<br>determined by the null transaction |                                                                                                                                             |  |

| S'Driving_value                                                                                                                                                                                               | the current value of the driver for S in the process containing the assignment statement to S                                               |  |

|                                                                         | nulation<br>edefii             | ned attril                                                                                                              | butes                                                                                 |                                                          |

|-------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------|

| Attributes of                                                           | scalar type                    | s:                                                                                                                      |                                                                                       |                                                          |

| Attribute                                                               |                                | lt type                                                                                                                 |                                                                                       | Result                                                   |

| TLeft                                                                   | same                           | as T                                                                                                                    |                                                                                       | leftmost value of T                                      |

| TRight                                                                  | same                           | as T                                                                                                                    |                                                                                       | rightmost value of T                                     |

| TLow                                                                    | same                           | as T                                                                                                                    |                                                                                       | least value in T                                         |

| THigh                                                                   | same                           | as T                                                                                                                    |                                                                                       | greatest value in T                                      |

| TAscending                                                              | boolea                         | n                                                                                                                       |                                                                                       | true if T is an ascending range, false otherwise         |

| Timage(x)                                                               | string                         |                                                                                                                         |                                                                                       | a textual representation of the value $\times$ of type T |

| T'Value(s)                                                              | base t                         | ype of T                                                                                                                |                                                                                       | value in T represented by the string s                   |

| Attribute<br>TPos(s)<br>TVal(x)                                         | Result type                    | nteger<br>of T                                                                                                          | Result position number of s in T value at position x in T (x is integer)              |                                                          |

| TSucc(s)                                                                | base type                      |                                                                                                                         | value at position one greater than s in T                                             |                                                          |

| TPred(s)<br>TLeftof(s)                                                  | base type                      |                                                                                                                         | value at position one less than s in T<br>value at position one to the left of s in T |                                                          |

| TRightof(s)                                                             | base type                      |                                                                                                                         | value at position one to the right of s in T                                          |                                                          |

|                                                                         |                                | and array-type o                                                                                                        |                                                                                       |                                                          |

| Attribute Result                                                        |                                |                                                                                                                         |                                                                                       |                                                          |

|                                                                         |                                | leftmost value in index range                                                                                           |                                                                                       |                                                          |

| A'Left(n)                                                               | rightmost value in index range |                                                                                                                         | ge of dimension n                                                                     |                                                          |

| A'Right(n)                                                              |                                |                                                                                                                         | of dimension n                                                                        |                                                          |

| A'Right(n)<br>A'Low(n)                                                  |                                | lower bound of index range                                                                                              |                                                                                       |                                                          |

| A'Right(n)                                                              |                                | upper bound of index range                                                                                              | of dimension n                                                                        |                                                          |

| A'Right(n)<br>A'Low(n)<br>A'High(n)<br>A'Range(n)                       |                                | upper bound of index range<br>index range of dimension n                                                                |                                                                                       |                                                          |

| A'Right(n)<br>A'Low(n)<br>A'High(n)<br>A'Range(n)<br>A'Reverse_range(n) |                                | upper bound of index range<br>index range of dimension n<br>reversed index range of dim                                 | ension n                                                                              |                                                          |

| A'Right(n)<br>A'Low(n)<br>A'High(n)<br>A'Range(n)                       |                                | upper bound of index range<br>index range of dimension n<br>reversed index range of dim<br>number of values in the n-th | ension n                                                                              |                                                          |