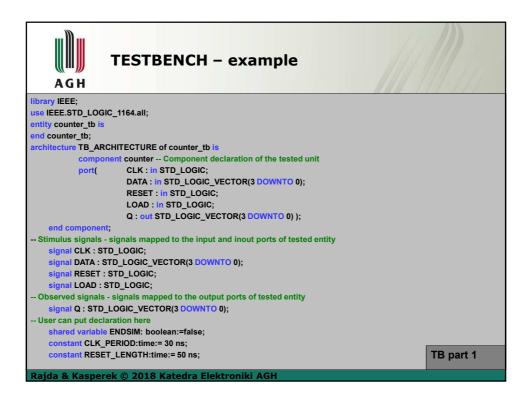

| AGH TEST                                        | BENCH – exar                          | nple                   | M         |

|-------------------------------------------------|---------------------------------------|------------------------|-----------|

| begin                                           |                                       | reset process          |           |

| Unit Under Test port map                        |                                       | RES: process           |           |

| UUT : counter                                   |                                       | begin RESET<='0';      |           |

| port map                                        |                                       | wait for RESET_LENGTH; |           |

| •                                               | => CLK,                               | RESET<='1';            |           |

|                                                 | => DATA,                              | wait;                  |           |

|                                                 | T => RESET,                           | end process;           |           |

|                                                 | => LOAD,                              | stimulus process       |           |

| Q => Q );                                       |                                       | STIM: process          |           |

| User can put stimulus here                      |                                       | begin                  |           |

| CLK_GEN: process                                |                                       | DATA<="0110";          |           |

| begin                                           |                                       | LOAD<='0';             |           |

| if ENDSIM=false then                            |                                       | wait for 350 ns;       |           |

| CLK <                                           | · · · · · · · · · · · · · · · · · · · | LOAD<='1';             |           |

|                                                 | or CLK_PERIOD/2;                      | wait for 50 ns;        |           |

| CLK <                                           | •                                     | LOAD<='0';             |           |

|                                                 | or CLK_PERIOD/2;                      | wait for 100 ns;       |           |

| else                                            |                                       | ENDSIM:=true;          |           |

| wait;                                           |                                       | wait;                  |           |

| end if;                                         |                                       | end process;           |           |

| end process;                                    |                                       |                        |           |

|                                                 | TB part 2                             | end TB_ARCHITECTURE;   | TB part 3 |

| Rajda & Kasperek © 2018 Katedra Elektroniki AGH |                                       |                        |           |

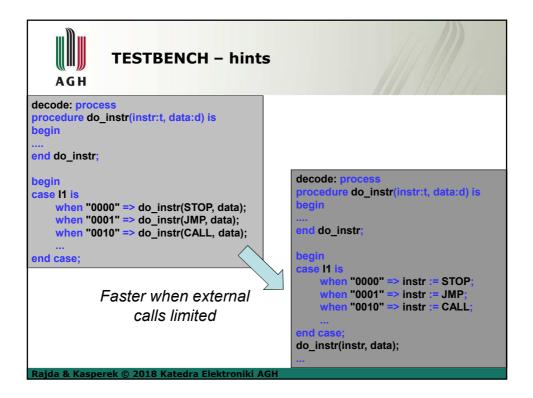

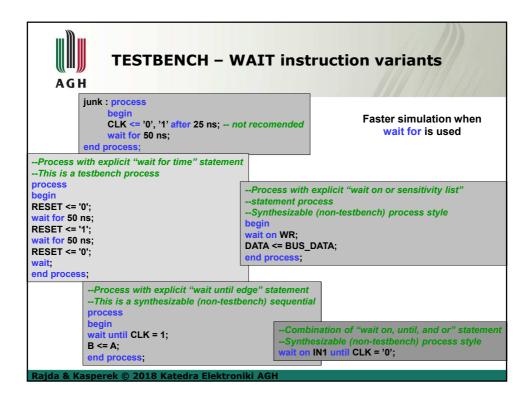

| TESTBENCH - hints                                                                                                                                                                                         |                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| one clock domain signals generation divider: process                                                                                                                                                      |                                                                                                                                                                                     |

| Begin<br>clk50 <= '0';<br>clk100 <= '0';<br>clk200 <= '0';<br>loop forever<br>for j in 1 to 2 loop<br>for k in 1 to 2 loop<br>wait on clk;<br>clk200 <= not clk200;<br>end loop;<br>clk100 <= not clk100; | different clock domain signals generation<br>separate process<br>Clock_A : process<br>begin<br>CLK_A <= '0';<br>wait for 200 ns;<br>CLK <= '1';<br>wait for 200 ns;<br>end process; |

| end loop;<br>clk50 <= not clk50;<br>end loop;<br>end process divider;                                                                                                                                     | Clock_B : process<br>begin<br>CLK_B <= '0';<br>wait for 33 ns;<br>CLK_B <= '1';<br>wait for 33 ns;<br>end process;                                                                  |