Module: Electronics & Telecomunication, 5rd year Programmable Logical Devices

# FPGA architectures Part 1

J.Kasperek & P.J.Raida © 2017 Katedra Elektroniki AGH

#### Agenda

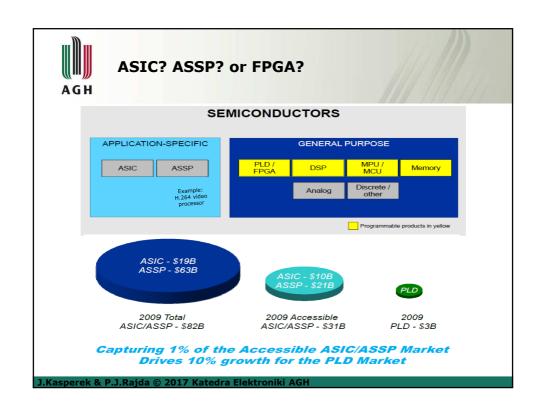

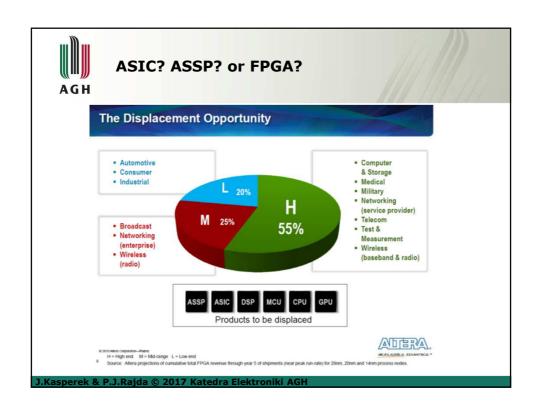

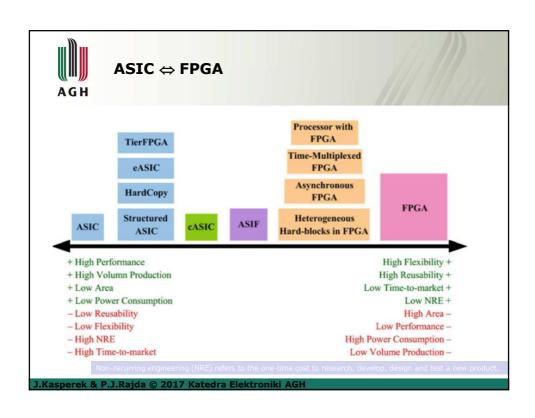

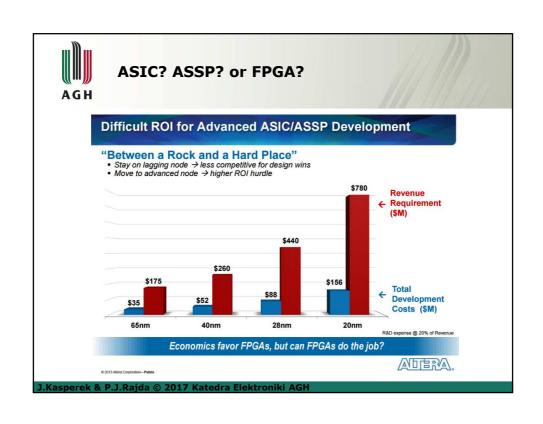

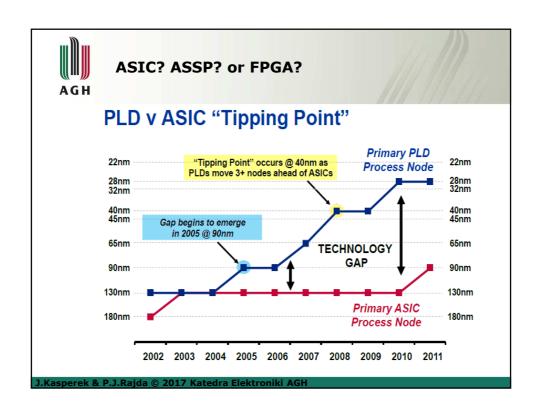

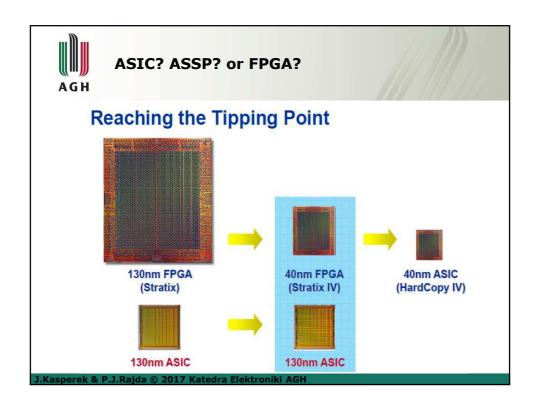

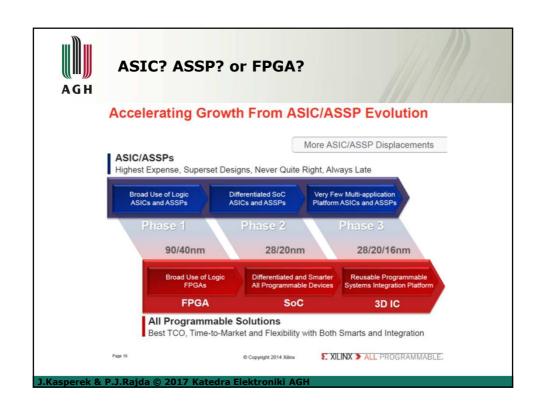

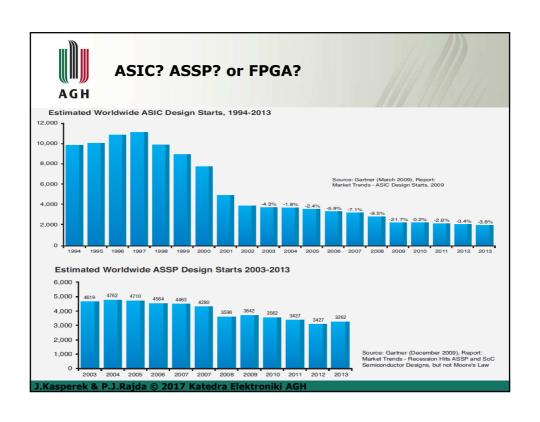

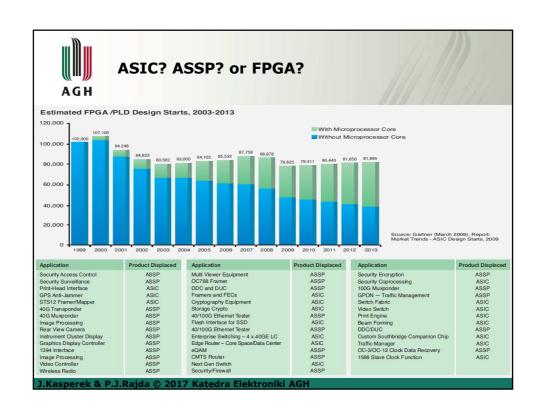

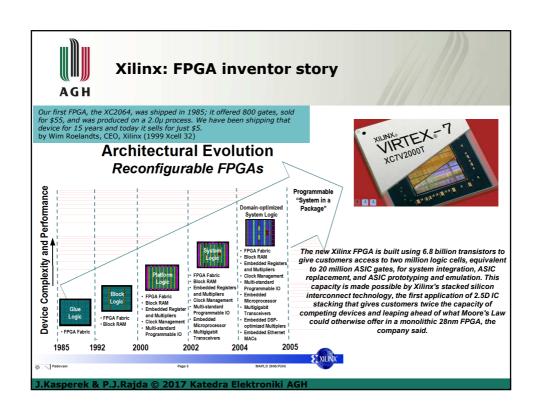

- ASIC vs ASSP vs FPGA

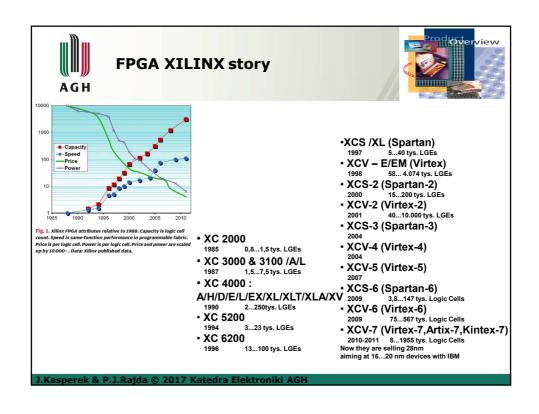

- FPGA devices

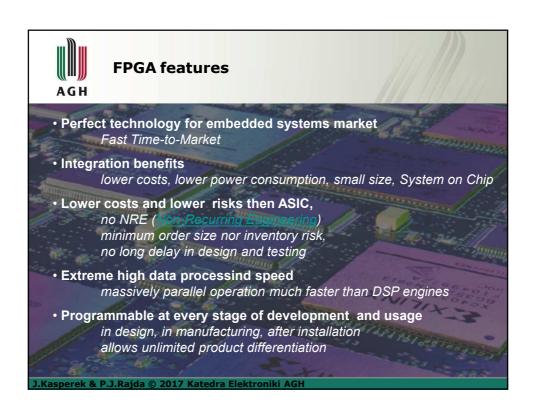

- Features

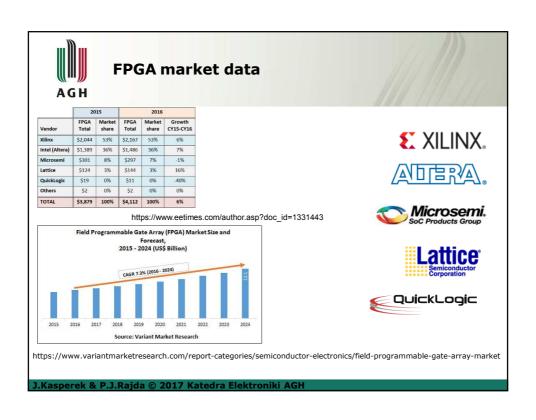

- Market data

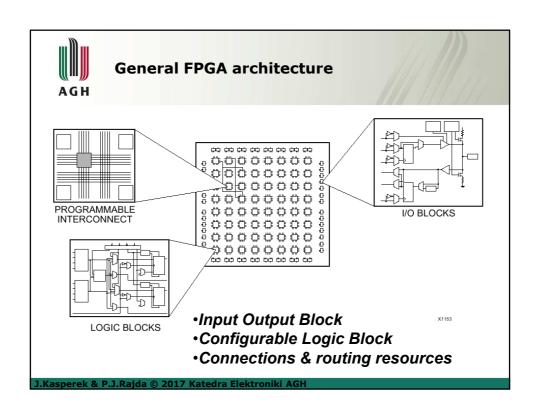

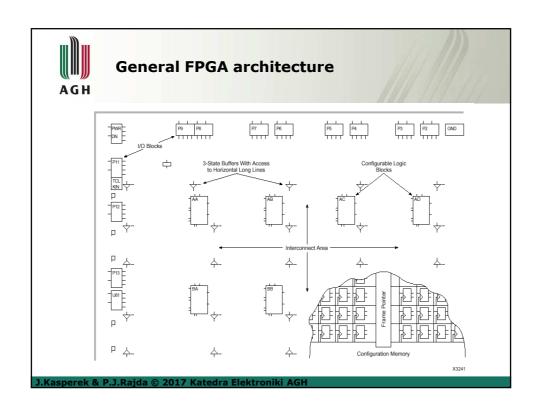

- FPGA architecture

- Xilinx FPGA

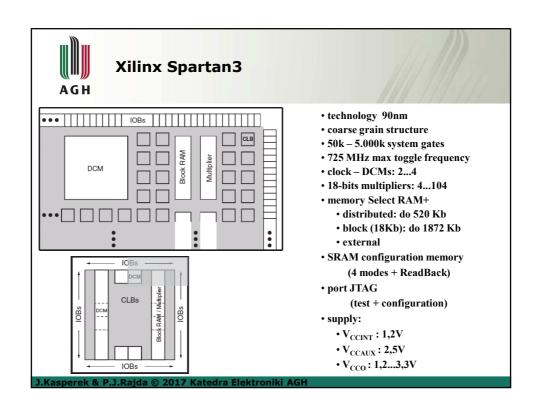

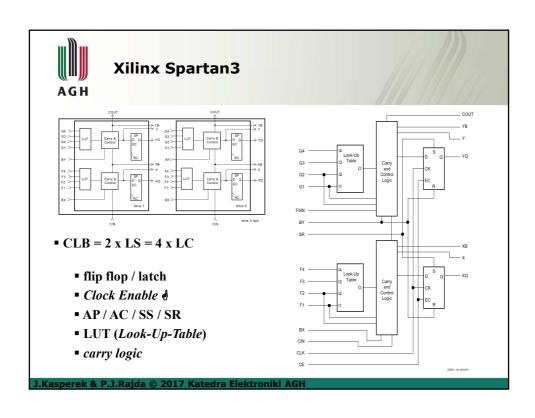

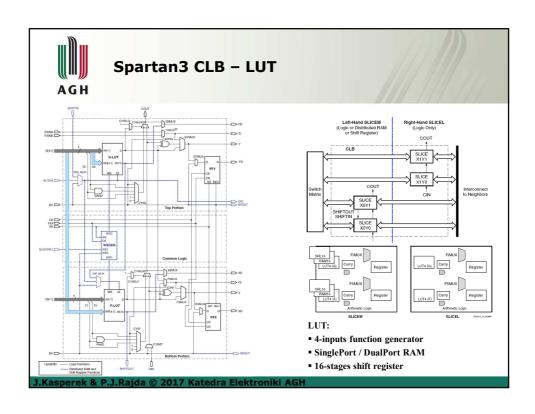

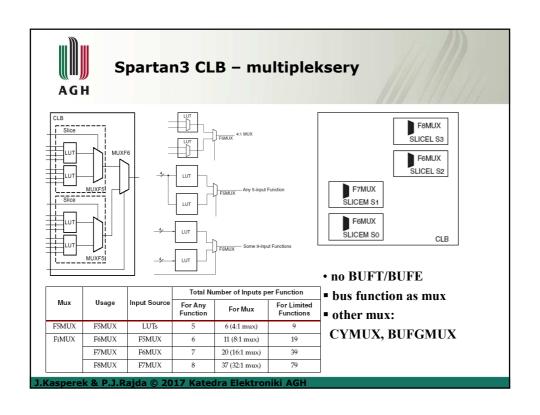

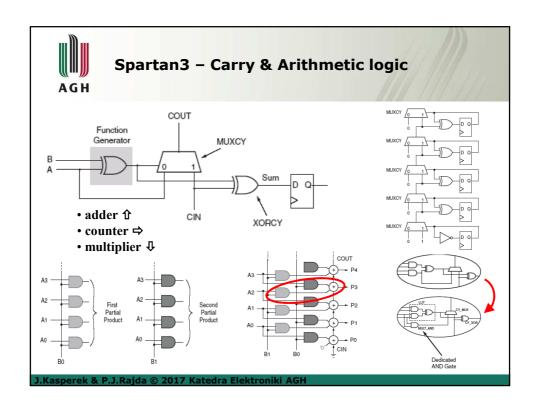

- Spartan 3

- · Spartan 6 Virtex 6

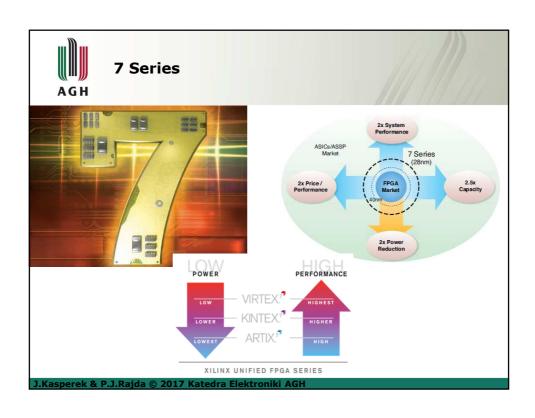

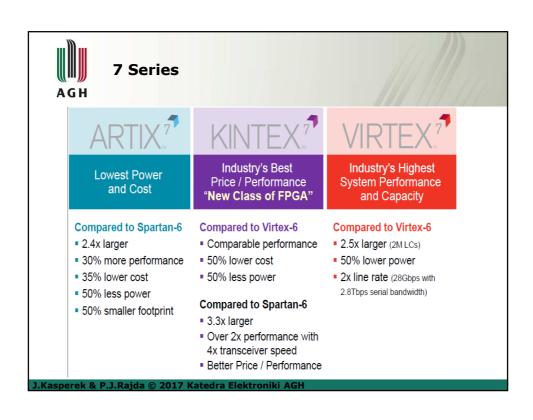

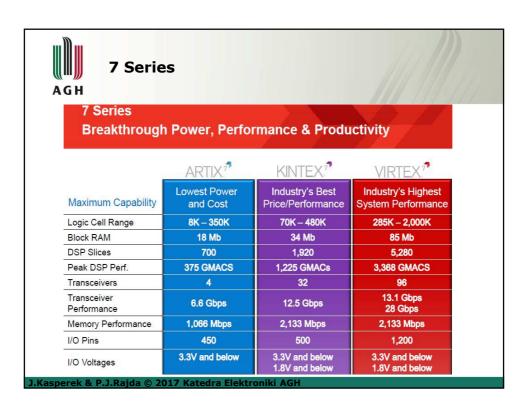

- 7 Series

- EasyPath

#### References

#### **WWW FPGA manufactures**

- Big labels (in alphabetical order)

- www.actel.com (Microsemi)

- www.altera.com (Intel)

- www.atmel.com (Microchip)

- www.latticesemi.com

- www.quicklogic.com

- www.xilinx.com (this lecture) (alliance with IBM since Nov 16, 2015)

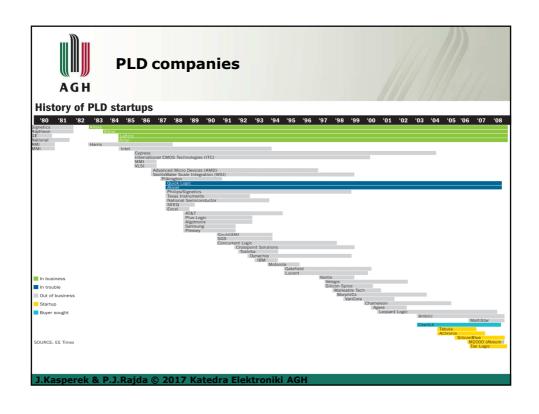

- FPGA startups

- http://www.achronix.com embedded FPGA (eFPGA)

- http://www.siliconbluetech.com acquired by LatticeSemiconductor

- http://www.tabula.com

⊗ Feb 2015 closed

- extras

- http://www.easic.com

- general

- www.eetimes.com/design/programmable-logic-designline

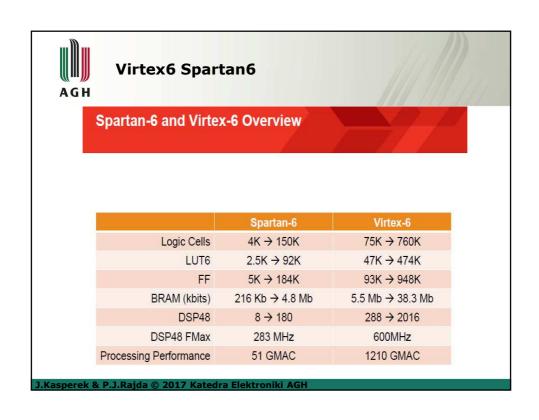

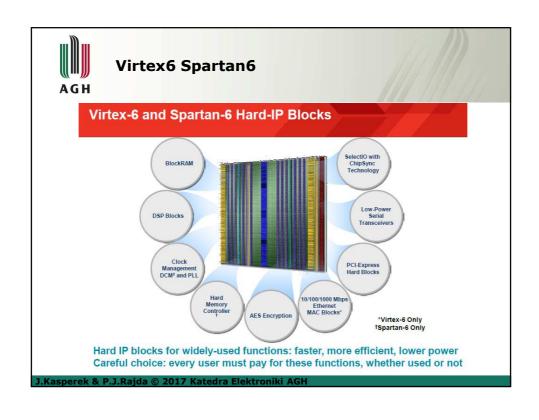

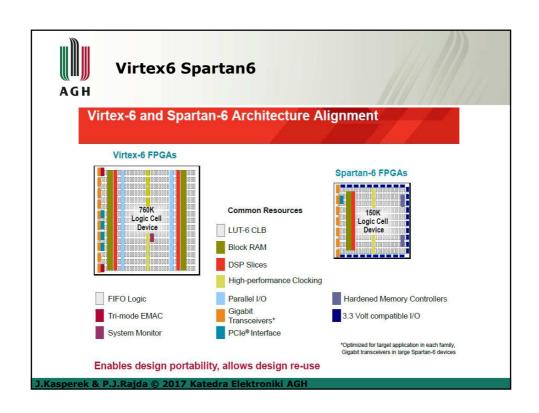

#### Virtex6 Spartan6

#### Virtex-6 and Spartan-6 FPGA Families

- Moore's Law

- Doubles the max capacity, compared to the previous generation

- Reduces cost per function

- Architecture and circuit innovations

- Increase speed and lower power consumption

- Wide range of capacity, applications, cost

- Virtex-6 and Spartan-6 FPGAs cover a 250: 1 capacity range

- At the high end: Virtex-6 covers a 10 : 1 ratio

- At the low end: Spartan-6 covers a 40 : 1 ratio

- The name always indicates the logic capacity: XC6V760 to XC6S4

- Virtex-6 and Spartan-6 share architecture, technology, software

- Different emphasis on cost, performance, power, size, packaging

#### Virtex6

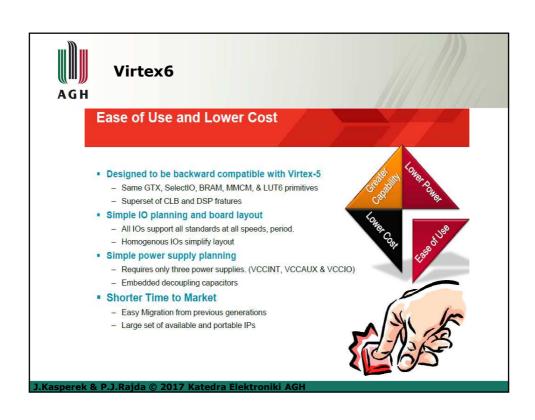

#### **Power Focus: Process and Circuit Innovation**

#### Low static power (controlled leakage)

- 3rd generations of Triple Oxide innovation

- Fast transistors wherever needed, low leakage everywhere else

- Speed without additional leakage:

- · Silicon Germanium (SiGe) implant layer

- Strained silicon

#### Low dynamic power

- Process shrink and low-K dielectric material

- Vccint = 1.0 V with 0.9 V option

- 20% lower power @ 10% lower speed

J.Kasperek & P.J.Raida © 2017 Katedra Elektroniki AGH

#### Virtex6

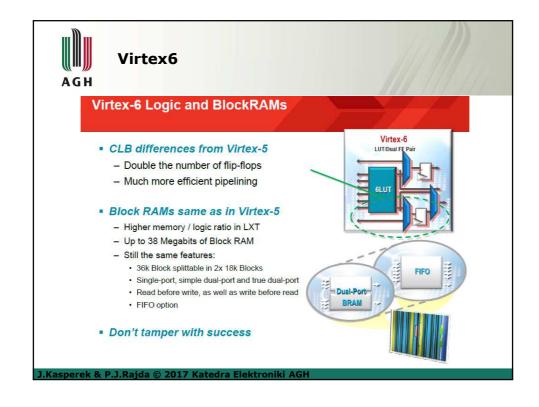

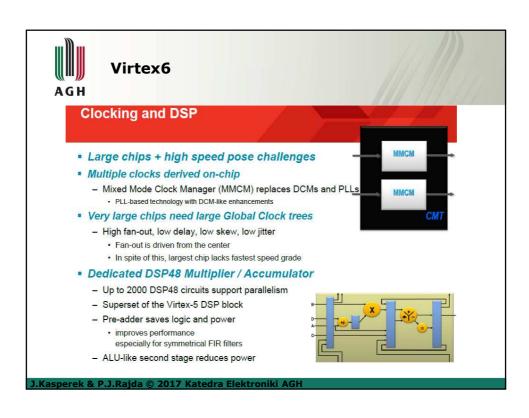

## Performance Improvements, Virtex-6 over Virtex-5

- Logic: 15% faster

- Advanced process, improved routing, faster pipelining

- Serial Transceivers: 86% higher total bandwidth

- Up to 72 transceivers delivering 580 Gbps in Virtex-6 HXT

- Compared to 48 transceivers delivering 312 Gbps in Virtex-5 TXT

- General-purpose I/O: 33% higher bandwidth

- Enables advanced memory interfaces (DDR3)

- Global clocking: 10% faster

- Lower skew, improved jitter, faster clock trees

- DSP bandwidth more than doubled

- Over 2,000 enhanced DSP slices

#### Spartan6

### **High-End Features in Spartan-6 FPGAs**

- Spartan-6 uses a 45-nm process, optimized for low power

- Low-cost FPGAs usually sacrifice performance

- But there are exceptions:

- DDR3 Controller

- DDR3 is lowest cost external memory, but needs a demanding interface

- DDR3 requires clock rate of >300 MHz (PLL on the memory device)

- Spartan-6 devices incorporate 2 or 4 dedicated DDR3 controllers.

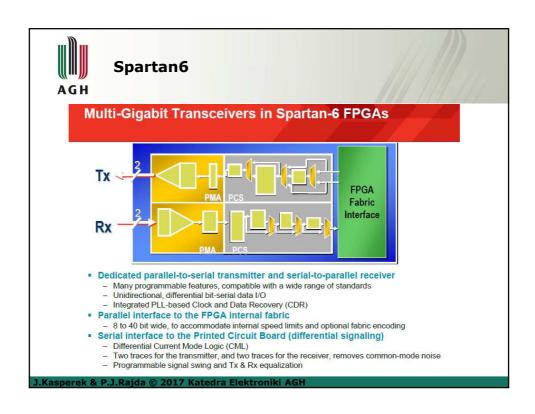

- Multi-Gigabit Transceivers @ up to 3.125 Gbps

- For bit-serial connectivity between devices, boards and boxes

- eliminates clock / data skew, reduces board area or cabling

- differential signals, 4 wires total, support high-bandwidth traffic,

J.Kasperek & P.J.Raida © 2017 Katedra Elektroniki AGH

#### Spartan6

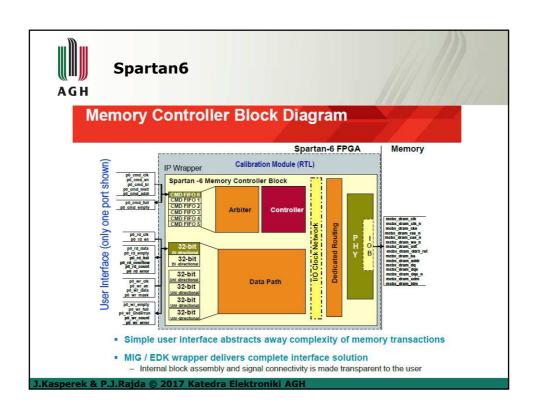

#### **Integrated Memory Controller in Spartan-6 FPGAs**

- Provides interfaces from low cost FPGAs to industry's most popular DRAM memories

- DDR, DDR2, DDR3, mobile DDR

- Up to 4 controllers in each Spartan-6 device

- Each of the these hard-coded controllers saves between 500 and 2000 LUTs versus soft solution

- Very important for cost-sensitive designs

- 12.8 Gbps bandwidth per controller

- 16-bit wide, 400MHz / 800Mbps operation

- Each controller interfaces to one DDR3 chip, no DIMMs

- Fast and easy implementation

- Wizard guided design flow

- Virtex-6 solution uses soft controller for flexibility

- Low-cost FPGA meets low-cost, but fast memory

#### 7 Series

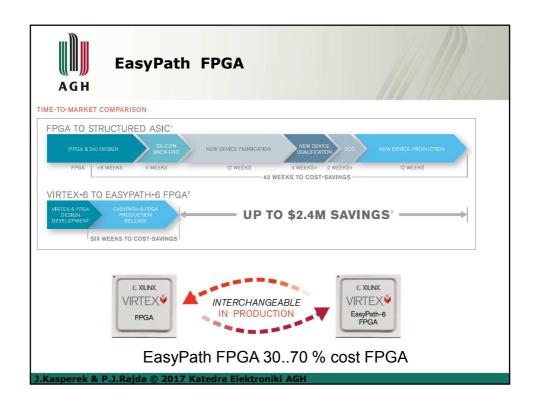

#### The Easy Way to Cost Savings

Xilinx EasyPath-6™ FPGAs offer a fast, simple and risk-free solution for cost reducing Virtex-6 FPGA designs. EasyPath-6 FPGAs deliver production volume devices in just six weeks with the lowest total product cost of any FPGA cost reduction solution. The cost savings are also available free of additional design constraints, re-engineering requirements, or re-layout of boards. EasyPath-6 FPGAs are architecturally equivalent to Virtex-6 FPGAs and match the FPGA datasheet specifications for functionality and timing. Unlike ASICs, the EasyPath-6 FPGA silicon requires no-requalification. Additionally, all Xilinx and third-party Intellectual Property (IP) for Virtex-6 FPGAs is supported by EasyPath-6 FPGAs without change or re-verification, and with no additional royalty, conversion or licensing fees.

#### COST REDUCTION OPTIONS

| COST DRIVERS        | EASYPATH-6 FPGA | STRUCTURED ASICS | STANDARD CELL ASICS |

|---------------------|-----------------|------------------|---------------------|

| Time-to-Market      | Fastest         | Slow             | Slowest             |

| Design Effort/Cost  | None            | Medium           | High                |

| Re-Spin Risk        | None            | High             | High                |

| Qualification Costs | None            | High             | High                |

| Opportunity Cost    | None            | High             | Highest             |

| NRE                 | Lowest          | High             | Highest             |